# 1 Mb Ultra-Low Power Serial SRAM

# Standard SPI Interface and Multiplex DUAL and QUAD Interface

#### Overview

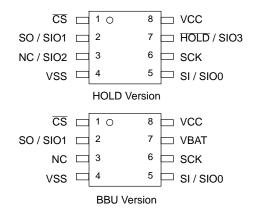

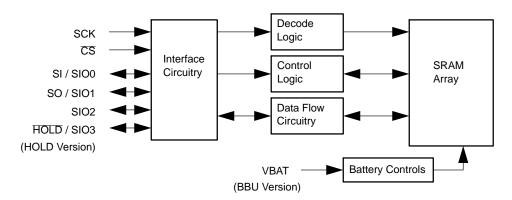

The ON Semiconductor serial SRAM family includes several integrated memory devices including this 1 Mb serially accessed Static Random Access Memory, internally organized as 128 K words by 8 bits. The devices are designed and fabricated using ON Semiconductor's advanced CMOS technology to provide both high-speed performance and low power. The devices operate with a single chip select  $(\overline{CS})$  input and use a simple Serial Peripheral Interface (SPI) protocol. In SPI mode, a single data-in (SI) and data-out (SO) line is used along with the clock (SCK) to access data within the device. In DUAL mode, two multiplexed data-in/data-out (SIO0-SIO1) lines are used and in QUAD mode, four multiplexed data-in/data-out (SIO0-SIO3) lines are used with the clock to access the memory. The devices can operate over a wide temperature range of -40°C to +85°C (+125°C for E-Temp) and are available in a 8-lead TSSOP package. The N01S830xA device has two different variations, a HOLD version that allows communication to the device to be paused and a battery back-up (BBU) version to be used with a battery to retain data when power is lost.

#### **Features**

- Power Supply Range: 2.5 to 5.5 V

- Very Low Typical Standby Current < 4 μA at +85°C

- Very Low Operating Current < 10 mA

- Simple Serial Interface

- Single-bit SPI Access

- DUAL-bit and QUAD-bit SPI-like Access

- Flexible Operating Modes

- Word Mode

- Page Mode

- Burst Mode (Full Array)

- High Frequency Read and Write Operation

- Clock Frequency up to 20 MHz

- Functional Options

- ◆ HOLD Pin for Pausing Operation

- ◆ VBAT Pin for Battery-Back up

- Built-in Write Protection (CS High)

- High Reliability

- Unlimited Write Cycles

- Temperature Ranges Supported

- Industrial (I):  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$

- Automotive (E):  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

- These Devices are Pb-Free and are RoHS Compliant

- ◆ Green TSSOP

# ON Semiconductor®

www.onsemi.com

TSSOP8 3x4.4 CASE 948BH

#### **PACKAGE CONFIGURATION**

#### ORDERING INFORMATION

| Device         | Package   | Shipping <sup>†</sup> |  |

|----------------|-----------|-----------------------|--|

| N01S830HAT22I  | TSSOP-8   | 100 Units / Tube      |  |

| N01S830BAT22I  | (Pb-Free) | 100 Offits / Tube     |  |

| N01S830HAT22IT | TSSOP-8   | 3000 / Tape           |  |

| N01S830BAT22IT | (Pb-Free) | & Reel                |  |

| N01S830HAT22E  | TSSOP-8   | 100 Units / Tube      |  |

| N01S830BAT22E  | (Pb-Free) | 100 Offits / Tube     |  |

| N01S830HAT22ET | TSSOP-8   | 3000 / Tape           |  |

| N01S830BAT22ET | (Pb-Free) | & Reel                |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

**Table 1. DEVICE OPTIONS**

| Device / Part Number | Power Supply     | Speed                               | Package | Temperature<br>Range | Function              |

|----------------------|------------------|-------------------------------------|---------|----------------------|-----------------------|

| N01S830HAT22         | HV 2.5 V – 5.5 V | 20 MHz for I-Temp,<br>16 MHz E-Temp | TSSOP-8 | I, E                 | HOLD                  |

| N01S830BAT22         | HV 2.5 V – 5.5 V | 20 MHz for I-Temp,<br>16 MHz E-Temp | TSSOP-8 | I, E                 | BBU – Battery Back-up |

#### **Table 2. PIN NAMES**

| Pin Name        | Pin Function                                                                      |

|-----------------|-----------------------------------------------------------------------------------|

| CS              | Chip Select                                                                       |

| SCK             | Serial Clock                                                                      |

| SI / SIO0       | Data Input – SPI mode<br>Data Input/Output 0 – DUAL and QUAD mode                 |

| SO / SIO1       | Data Output – SPI mode<br>Data Input/Output 1 – DUAL and QUAD mode                |

| NC / SIO2       | No Connect – SPI and DUAL mode<br>Data Input/Output 2 – QUAD mode                 |

| HOLD / SIO3     | HOLD Version<br>HOLD Input – SPI and DUAL mode<br>Data Input/Output 3 – QUAD mode |

| VBAT            | BBU Version<br>Battery Supply – SPI and DUAL mode                                 |

| V <sub>CC</sub> | Power                                                                             |

| V <sub>SS</sub> | Ground                                                                            |

Figure 1. Functional Block Diagram

### **Table 3. CONTROL SIGNAL DESCRIPTIONS**

| Signal | Mode<br>Used | Name            | Description                                                                                                                                                                                                                                                                                                                                            |

|--------|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS     | All          | Chip Select     | A low level selects the device and a high level puts the device in standby mode. If $\overline{CS}$ is brought high during a program cycle, the cycle will complete and then the device will enter standby mode. When $\overline{CS}$ is high, SO is in high-Z. $\overline{CS}$ must be driven low after power-up prior to any sequence being started. |

| SCK    | All          | Serial Clock    | Synchronizes all activities between the memory and controller. All incoming addresses, data and instructions are latched on the rising edge of SCK. Data out is updated after the falling edge of SCK.                                                                                                                                                 |

| SI     | SPI          | Serial Data In  | Receives instructions, addresses and data on the rising edge of SCK.                                                                                                                                                                                                                                                                                   |

| SO     | SPI          | Serial Data Out | Data is transferred out after the falling edge of SCK.                                                                                                                                                                                                                                                                                                 |

**Table 3. CONTROL SIGNAL DESCRIPTIONS**

| Signal   | Mode<br>Used    | Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

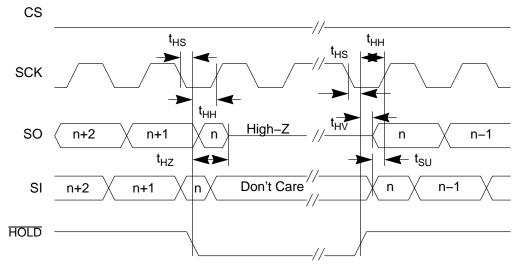

| HOLD     | SPI and<br>DUAL | Hold                          | A high level is required for normal operation. Once the device is selected and a serial sequence is started, this input may be taken low to pause serial communication without resetting the serial sequence. The pin must be brought low while SCK is low for immediate use. If SCK is not low, the HOLD function will not be invoked until the next SCK high to low transition. The device must remain selected during this sequence. SO is high-Z during the Hold time and SI and SCK are inputs are ignored. To resume operations, HOLD must be pulled high while the SCK pin is low. Lowering the HOLD input at any time will take to SO output to High-Z. |

| VBAT     | SPI and<br>DUAL | Battery Voltage               | Provides the battery power connection to retain data in battery backed mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SIO0 - 1 | DUAL            | Serial Data<br>Input / Output | Receives instructions, addresses and data on the rising edge of SCK. Data is transferred out after the falling edge of SCK. The instruction must be set after power-up to enable the DUAL access mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SIO0 - 3 | QUAD            | Serial Data<br>Input / Output | Receives instructions, addresses and data on the rising edge of SCK. Data is transferred out after the falling edge of SCK. The instruction must be set after power-up to enable the QUAD access mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### **Basic Operation**

The 1 Mb serial SRAM is designed to interface directly with a standard Serial Peripheral Interface (SPI) common on many standard micro-controllers in the default state. It may also interface with other non-SPI ports by programming discrete I/O lines to operate the device.

The serial SRAM contains an 8-bit instruction register and is accessed via the SI pin. The  $\overline{CS}$  pin must be low and the  $\overline{HOLD}$  pin must be high for the entire operation. Data is sampled on the first rising edge of SCK after  $\overline{CS}$  goes low. If the clock line is shared, the user can assert the  $\overline{HOLD}$  input and place the device into a Hold mode. After releasing the  $\overline{HOLD}$  pin, the operation will resume from the point where it was held. The Hold operation is only supported in SPI and DUAL modes.

By programming the device through a command instruction, the dual and quad access modes may be initiated. In these modes, multiplexed I/O lines take the place of the SPI SI and SO pins and along with the  $\overline{CS}$  and SCK control the device in a SPI-like, two bit (DUAL) and four bit (QUAD) wide serial manner. Once the device is put into either the DUAL or QUAD mode, the device will remain operating in that mode until powered down or the Reset Mode operation is programmed.

The following table contains the possible instructions and formats. All instructions, addresses and data are transferred MSB first and LSB last.

**Table 4. INSTRUCTION SET**

| Instruction | Command | Description                                                 |

|-------------|---------|-------------------------------------------------------------|

| READ        | 03h     | Read data from memory starting at selected address          |

| WRITE       | 02h     | Write (program) data to memory starting at selected address |

| EQIO        | 38h     | Enable QUAD I/O access                                      |

| EDIO        | 3Bh     | Enable DUAL I/O access                                      |

| RSTQIO      | FFh     | Reset from QUAD and DUAL to SPI I/O access                  |

| RDMR        | 05h     | Read mode register                                          |

| WRMR        | 01h     | Write mode register                                         |

#### **DEVICE OPERATIONS**

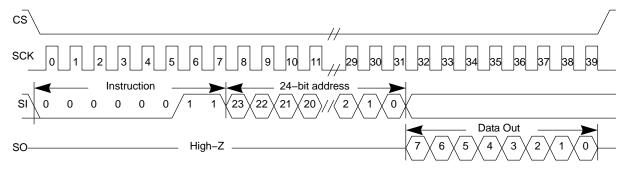

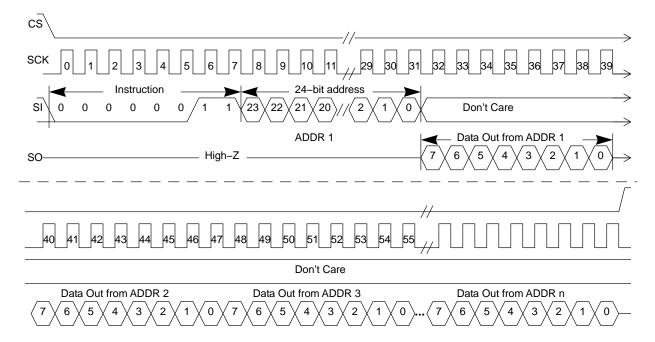

#### **Read Operation**

The serial SRAM Read operation is started by by enabling  $\overline{CS}$  low. First, the 8-bit Read instruction is transmitted to the device through the SI (or SIO0-3) pin(s) followed by the 24-bit address with the 7 MSBs of the address being "don't care" bits and ignored. In SPI mode, after the READ instruction and address bits are sent, the data stored at that address in memory is shifted out on the SO pin after the output valid time. Additional "dummy" clock cycles (four in DUAL and two in QUAD) are required to follow the instruction and address inputs prior to the data being driven out on the SIO0-3 pins while operating in these two modes.

By continuing to provide clock cycles to the device, data can continue to be read out of the memory array in sequentially. The internal address pointer is automatically incremented to the next higher address after each byte of data is read out until the highest memory address is reached. When the highest memory address is reached, 1FFFFh, the address pointer wraps to the address 00000h. This allows the read cycles to be continued indefinitely. All Read operations are terminated by pulling  $\overline{\text{CS}}$  high.

Figure 2. SPI Read Sequence (Single Byte)

Figure 3. SPI Read Sequence (Sequential Bytes)

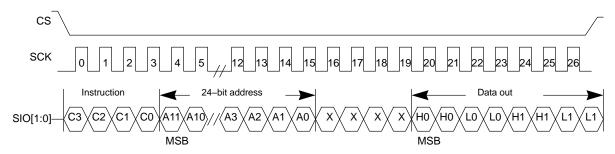

**Notes:** C[3:0] = 03h

H0 = 2 high order bits of data byte 0 L0 = 2 low order bits of data byte 0 H1 = 2 high order bits of data byte 1 L1 = 2 low order bits of data byte 1

Figure 4. DUAL Read Sequence

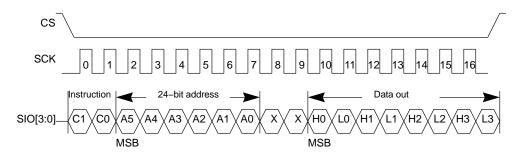

**Notes:** C[1:0] = 03h

H0 = 4 high order bits of data byte 0 L0 = 4 low order bits of data byte 0 H1 = 4 high order bits of data byte 1 L1 = 4 low order bits of data byte 1

Figure 5. QUAD Read Sequence

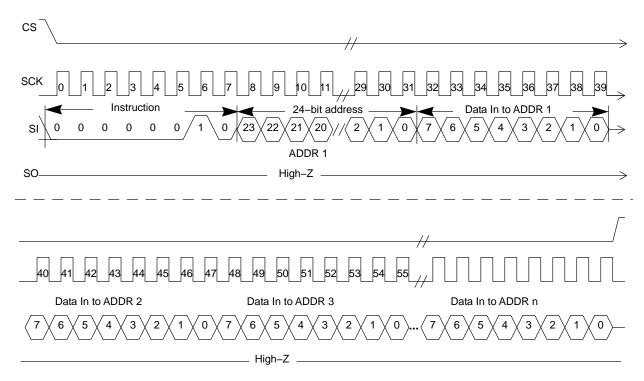

#### **Write Operation**

The serial SRAM WRITE is selected by enabling  $\overline{\text{CS}}$  low. First, the 8-bit WRITE instruction is transmitted to the device followed by the 24-bit address with the 7 MSBs being don't care. After the WRITE instruction and addresses are sent, the data to be stored in memory is shifted in on the SI pin.

If operating in page mode, after the initial word of data is shifted in, additional data words can be written as long as the address requested is sequential on the same page. Simply write the data on SI pin and continue to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each word of data is written in. This can be continued for the entire page length of 32 words long. At the end of the page, the addresses pointer will be wrapped to the 0 word address within the

page and the operation can be continuously looped over the 32 words of the same page. The new data will replace data already stored in the memory locations.

If operating in burst mode, after the initial word of data is shifted in, additional data words can be written to the next sequential memory locations by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each word of data is read out. This can be continued for the entire array and when the highest address is reached, 1FFFFh, the address counter wraps to the address 00000h. This allows the burst write cycle to be continued indefinitely. Again, the new data will replace data already stored in the memory locations.

All WRITE operations are terminated by pulling  $\overline{CS}$  high.

Figure 6. SPI Write Sequence

H0 = 2 high order bits of data byte 0 L0 = 2 low order bits of data byte 0 H1 = 2 high order bits of data byte 1 L1 = 2 low order bits of data byte 1

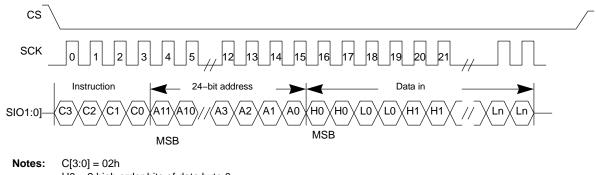

Figure 7. DUAL Write Sequence

**Notes:** C[1:0] = 02h

H0 = 4 high order bits of data byte 0 L0 = 4 low order bits of data byte 0 H1 = 4 high order bits of data byte 1 L1 = 4 low order bits of data byte 1

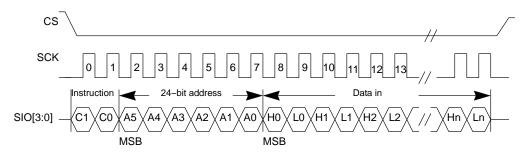

Figure 8. QUAD Write Sequence

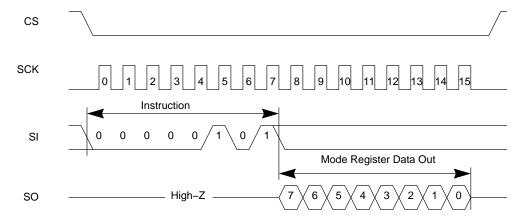

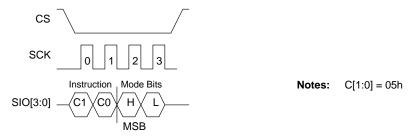

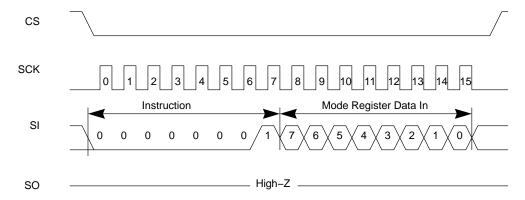

## **READ Mode Register (RDMR)**

This instruction provides the ability to read the mode register. The register may be read at any time including during a Write operation. The Read Mode Register operation is executed by driving  $\overline{\text{CS}}$  low, then sending the

RDMR instruction to the device. Immediately after the instruction, the device outputs data on the SO (SIO0-3) pin(s). To complete the operation, drive  $\overline{CS}$  high to terminate the register read.

Figure 9. SPI Read Mode Register Sequence (RDMR)

Figure 10. DUAL Read Mode Register Sequence (RDMR)

Figure 11. QUAD Read Mode Register Sequence (RDMR)

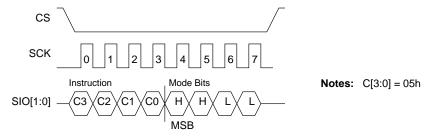

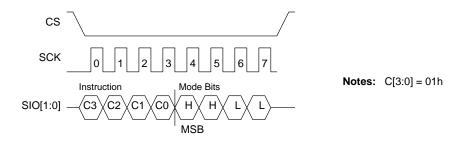

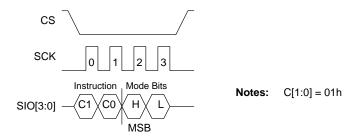

#### Write Mode Register (WRMR)

This instruction provides the ability to write the mode register. The Write Mode Register operation is executed by driving  $\overline{\text{CS}}$  low, then sending the WRMR instruction to the

device. Immediately after the instruction, the data is driven to the device on the SO (SIO0-3) pin(s). To complete the operation, drive  $\overline{CS}$  high to terminate the register write.

Figure 12. SPI Write Mode Register Sequence

Figure 13. DUAL Write Mode Register Sequence

Figure 14. QUAD Write Mode Register Sequence

#### **Table 5. MODE REGISTER**

| Bit |                            | Function                      |  |

|-----|----------------------------|-------------------------------|--|

| 0   |                            | unction                       |  |

|     | 1 = Ho                     | ld function disabled          |  |

|     | 0 = Ho                     | ld function enabled (Default) |  |

| 1   | Reserv                     | ved                           |  |

| 2   | Reserv                     | ved                           |  |

| 3   | Reserved                   |                               |  |

| 4   | Reserved                   |                               |  |

| 5   | Reserved                   |                               |  |

| 6   | Operat                     | ing Mode                      |  |

|     | Bit 7 Bit 6                |                               |  |

|     | 0 0 = Word Mode            |                               |  |

| 7   | 1 0 = Page Mode            |                               |  |

|     | 0 1 = Burst Mode (Default) |                               |  |

|     | 1                          | 1 = Reserved                  |  |

#### **Power-Up State**

The serial SRAM enters a know state at power-up time. The device is in low-power standby state with  $\overline{CS} = 1$ . A low level on  $\overline{CS}$  is required to enter a active state.

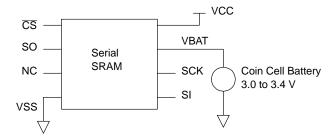

#### **Battery Back-Up Operation**

The Battery Back-Up function is available on the BBU version of the serial SRAM. This version of the SRAM cannot operate in the QUAD mode since the SIO3 input is used for the VBAT connection. A standard coin cell battery should be connected to the VBAT pin. On chip circuitry monitors the V<sub>CC</sub> pin and when it is determined that the main V<sub>CC</sub> power supply is turning off, the device automatically switches the memory array to VBAT power input. When in battery back-up mode and 3.0 to 3.4 V power supplied to the VBAT input, memory data is retained in the SRAM array and all existing interface and operating mode information is retained.

Figure 15. Battery Back-Up Version Schematics

**Table 6. ABSOLUTE MAXIMUM RATINGS**

| Item                                                          | Symbol              | Rating                        | Units |

|---------------------------------------------------------------|---------------------|-------------------------------|-------|

| Voltage on any pin relative to V <sub>SS</sub>                | V <sub>IN,OUT</sub> | -0.3 to V <sub>CC</sub> + 0.3 | V     |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> | V <sub>CC</sub>     | -0.3 to 5.5                   | V     |

| Power Dissipation                                             | P <sub>D</sub>      | 500                           | mW    |

| Storage Temperature                                           | T <sub>STG</sub>    | -40°C to 125°C                | °C    |

| Ambient Temperature Under Bias                                | T <sub>A</sub>      | -40°C to +125°C               | °C    |

| Soldering Temperature and Time                                | T <sub>SOLDER</sub> | 260°C, 10 sec                 | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 7. OPERATING CHARACTERISTICS** (Industrial (I):  $T_A = -40^{\circ}$ C to +85°C, Automotive (E):  $T_A = -40^{\circ}$ C to +125°C)

| Item                   | Symbol          | Test Conditions                                                                                                                              | Min                   | Typ (Note 1) | Max                   | Units |

|------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|-----------------------|-------|

| Supply Voltage         | V <sub>CC</sub> |                                                                                                                                              | 2.5                   |              | 5.5                   | V     |

| Data Retention Voltage | $V_{DR}$        |                                                                                                                                              | 1.0                   |              |                       | V     |

| Input High Voltage     | V <sub>IH</sub> |                                                                                                                                              | 0.7 V <sub>CC</sub>   |              | V <sub>CC</sub> + 0.3 | V     |

| Input Low Voltage      | V <sub>IL</sub> |                                                                                                                                              | -0.3                  |              | 0.1 V <sub>CC</sub>   | V     |

| Output High Voltage    | V <sub>OH</sub> | $I_{OH} = -0.4 \text{ mA}$                                                                                                                   | V <sub>CC</sub> - 0.2 |              |                       | V     |

| Output Low Voltage     | V <sub>OL</sub> | I <sub>OL</sub> = 1 mA                                                                                                                       |                       |              | 0.2                   | V     |

| Input Leakage Current  | ILI             | $\overline{\text{CS}} = \text{V}_{\text{CC}},  \text{V}_{\text{IN}} = 0 \text{ to V}_{\text{CC}}$                                            |                       |              | 1.0                   | μΑ    |

| Output Leakage Current | I <sub>LO</sub> | $\overline{\text{CS}} = V_{\text{CC}}, V_{\text{OUT}} = 0 \text{ to } V_{\text{CC}}$                                                         |                       |              | 1.0                   | μΑ    |

| Operating Current      | Icc             | f = 20 MHz, I <sub>OUT</sub> = 0, SPI / DUAL                                                                                                 |                       |              | 10                    | mA    |

|                        |                 | f = 20 MHz, I <sub>OUT</sub> = 0, QUAD                                                                                                       |                       |              | 20                    |       |

| Standby Current        | I <sub>SB</sub> | $\overline{\text{CS}} = \text{V}_{\text{CC}},  \text{V}_{\text{IN}} = \text{V}_{\text{SS}}  \text{or}  \text{V}_{\text{CC}},  \text{I-Temp}$ |                       | 4            | 10                    | μΑ    |

|                        |                 | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{ V}_{\text{IN}} = \text{V}_{\text{SS}} \text{ or V}_{\text{CC}}, \text{ E-Temp}$         |                       |              | 20                    |       |

<sup>1.</sup> Typical values are measured at  $V_{CC} = V_{CC}$  Typ.,  $T_A = 25$ °C and are not 100% tested.

# Table 8. CAPACITANCE (Note 2)

| Item              | Symbol           | Symbol Test Conditions                                               |  | Max | Units |

|-------------------|------------------|----------------------------------------------------------------------|--|-----|-------|

| Input Capacitance | C <sub>IN</sub>  | $V_{IN} = 0 \text{ V, f} = 1 \text{ MHz, } T_A = 25^{\circ}\text{C}$ |  | 7   | pF    |

| I/O Capacitance   | C <sub>I/O</sub> | $V_{IN} = 0 \text{ V, f} = 1 \text{ MHz, } T_A = 25^{\circ}\text{C}$ |  | 7   | pF    |

<sup>2.</sup> These parameters are verified in device characterization and are not 100% tested.

# **Table 9. TIMING TEST CONDITIONS**

| Item                                     | Value                                      |

|------------------------------------------|--------------------------------------------|

| Input Pulse Level                        | 0.1 V <sub>CC</sub> to 0.9 V <sub>CC</sub> |

| Input Rise and Fall Time                 | 5 ns                                       |

| Input and Output Timing Reference Levels | 0.5 V <sub>CC</sub>                        |

| Output Load                              | CL = 30 pF                                 |

| Operating Temperature                    | Industrial (I): -40°C to +85°C             |

|                                          | Automotive (E): -40°C to +125°C            |

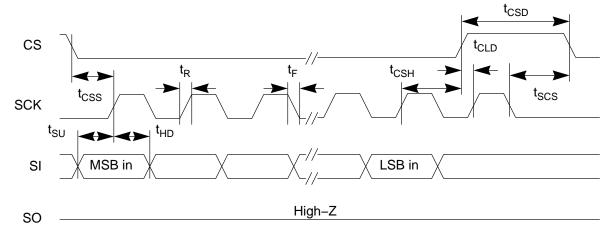

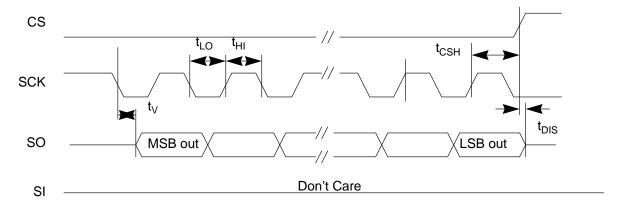

# Table 10. TIMING

|                             |                   | I <b>-</b> T | emp | E-T | emp |       |

|-----------------------------|-------------------|--------------|-----|-----|-----|-------|

| Characteristic              | Symbol            | Min          | Max | Min | Max | Units |

| Clock Frequency             | f <sub>CLK</sub>  |              | 20  |     | 16  | MHz   |

| Clock Rise Time             | t <sub>R</sub>    |              | 20  |     | 20  | ns    |

| Clock Fall Time             | t <sub>F</sub>    |              | 20  |     | 20  | ns    |

| Clock High Time             | t <sub>HI</sub>   | 25           |     | 32  |     | ns    |

| Clock Low Time              | t <sub>LO</sub>   | 25           |     | 32  |     | ns    |

| Clock Delay Time            | t <sub>CLD</sub>  | 25           |     | 32  |     | ns    |

| CS Setup Time               | t <sub>CSS</sub>  | 25           |     | 32  |     | ns    |

| CS Hold Time                | t <sub>CSH</sub>  | 50           |     | 50  |     | ns    |

| CS Disable Time             | t <sub>CSD</sub>  | 25           |     | 32  |     | ns    |

| SCK to CS                   | t <sub>SCS</sub>  | 5            |     | 5   |     | ns    |

| Data Setup Time             | t <sub>SU</sub>   | 10           |     | 10  |     | ns    |

| Data Hold Time              | t <sub>HD</sub>   | 10           |     | 10  |     | ns    |

| Output Valid From Clock Low | t <sub>V</sub>    |              | 25  |     | 32  | ns    |

| Output Hold Time            | t <sub>HO</sub>   | 0            |     | 0   |     | ns    |

| Output Disable Time         | t <sub>RDIS</sub> |              | 20  |     | 20  | ns    |

| HOLD Setup Time             | t <sub>HS</sub>   | 10           |     | 10  |     | ns    |

| HOLD Hold Time              | tнн               | 10           |     | 10  |     | ns    |

| HOLD Low to Output High-Z   | t <sub>HZ</sub>   | 10           |     | 10  |     | ns    |

| HOLD High to Output Valid   | t <sub>HV</sub>   |              | 50  |     | 50  | ns    |

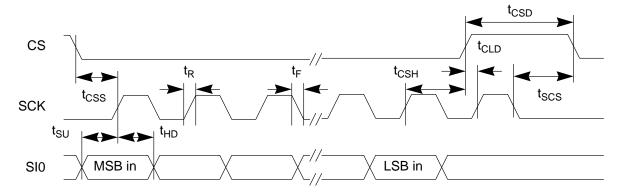

Figure 16. SPI Input Timing

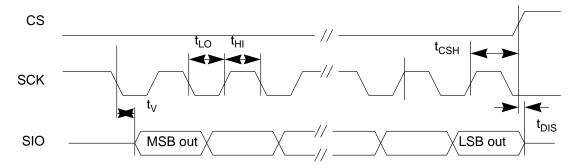

Figure 17. SPI Output Timing

Figure 18. SPI Hold Timing

Figure 19. QUAD Input Timing

Figure 20. QUAD Output Timing

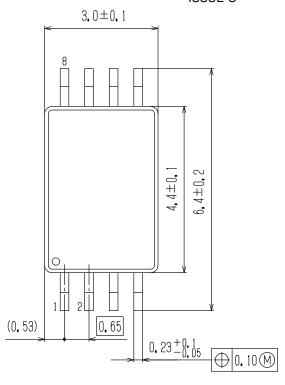

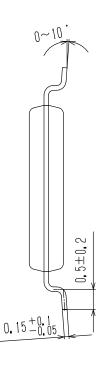

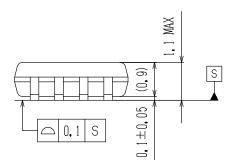

#### PACKAGE DIMENSIONS

#### TSSOP8 3x4.4 / TSSOP8 (225 mil)

CASE 948BH ISSUE O

ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding

#### **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# **ON Semiconductor:**

N01S830HAT22IT N01S830HAT22I N01S830BAT22I N01S830BAT22IT